- #FPGA HOW IT WORKS HOW TO#

- #FPGA HOW IT WORKS VERIFICATION#

- #FPGA HOW IT WORKS CODE#

- #FPGA HOW IT WORKS DOWNLOAD#

script, which means once and for all.įive. The recommended textbooks are Writing Testbenches using SystemVerilog, The UVM Primer, and System Verilog 1800-2012 Syntax Manual.Īfter mastering TCL/TK, you can learn virtual Jtag (ISE also has similar tools) to make your own debugging tools, in addition, if you have time, it is better to learn a python.

#FPGA HOW IT WORKS VERIFICATION#

If you are doing IC verification, you must master System Verilog and Verification Methodology (UVM). In addition, you can also use System Verilog instead of testbench, which will be a bit more efficient. the file comparator Beyond Compare is also a relatively common tool.

#FPGA HOW IT WORKS CODE#

You may back up your code manually, but professionals use version controllers, so it is important to master GIT in order to improve efficiency. modelsim is also a common simulation tool, learn TCL/TK to write your own DO file to make simulation become automated, the recommended textbook is "TCL/TK Introductory Classic". So it is recommended to use the function of code snippet in Sublime text editor to reduce repetitive work. If there is no understanding of the place can be skipped for the time being, because this part also needs a sufficient amount of practice, in order to have a deeper understanding.įour, learn to improve development efficiency.īecause the editor of Quartus and ISE is too weak, which affects the development efficiency. Learn to speed up the compilation (incremental compilation, LogicLock), static timing analysis (timequest), embedded logic analyzer (signaltap) is the pass. The recommended textbooks are "The Definitive Guide to FPGAs", "IP Cores - Digital Logic Design Ideas", and the basic and advanced chapters of the second edition of Altera FPGA/CPLD Design.

#FPGA HOW IT WORKS HOW TO#

This time, you have to learn to synchronize the design principles, optimize the circuit, whether speed first or area first, how the clock tree should be designed, how to synchronize two heterodyne clocks, and so on. You may find that the circuit you synthesized, although correct, but there are many warnings. Three, master the design method and design principles.

The recommended textbook is "WRITING TESTBENCHES Functional Verification of HDL Models". Here first master the simple testbench can be.

#FPGA HOW IT WORKS DOWNLOAD#

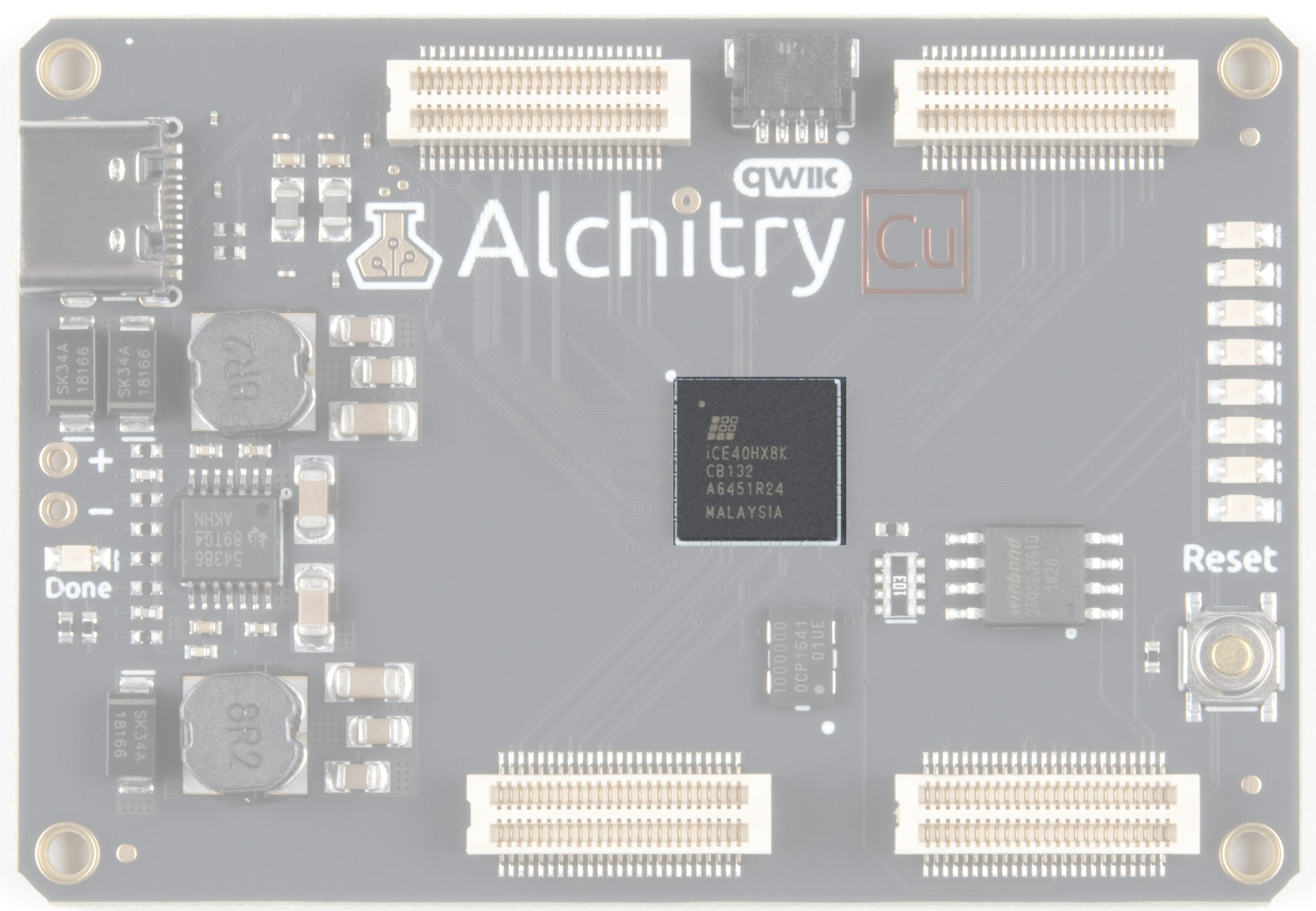

Here you do not have to download the code every time the compilation passes, we use modelsim simulation (in addition to QuestaSim, NC verilog, Diamond's Active-HDL, VCS, Debussy/Verdi and other simulation tools), if the simulation can not pass then there is no need to download, certainly not. Don't buy a development board before you master HDL, because you won't be able to use it if you buy it. You need a development board, either Altera's cyclone IV series, or Xilinx's Spantan 6. At this stage, all you have to do is: given a specification requirement or timing diagram, you can design a circuit in HDL to implement it. The recommended textbook is Xia Lao "Verilog Digital System Design Tutorial" (third edition). Now, you can design some digital circuits, such as traffic lights, electronic piano, DDS, etc. Two, independently complete the design of small and medium-scale digital circuits. You can write a three-stage state machine without reading the book and then you can move to the next stage. At this stage, the recommended textbook is "Verilog Legend", "Verilog HDL Advanced Digital Design" or "VHDL for Logic Synthesis". HDL is a hardware description language, highlighting the hardware as a feature, so think about HDL with the thinking of digital electricity, rather than using C or other high-level language, if you can not understand this statement, you can read "What is hardware and what is software. After compiling the code, open the RTL diagram and see what kind of circuit is synthesized. The meaning of the code copy is to familiarize yourself with the syntax rules and compiler (the compiler here is the silicon compiler also called synthesizer, commonly used compilers are: Quartus, ISE, Vivado, Design Compiler, Synopsys VCS, iverilog, Lattice Diamond, Microsemi/ Actel's Libero, Synplify pro), and then imitate the writing, and finally write without reading the book. Next, first find this example to copy the code. Of course, your mind can turn over, you can also choose verilog, after all, in the country verilog used more. because verilog is too much like C, it is easy to confuse, and finally you will find that you spend a lot of time to distinguish between the two languages, rather than learning how to use it. Then you can choose verilog or VHDL, C language foundation, it is recommended to choose VHDL. Not yet learned the number of electricity first learn the number of electricity.

One, the first thing to get started is to master HDL (HDL = verilog + VHDL).

0 kommentar(er)

0 kommentar(er)